#C51 keil code

The XDATA RAM and CODE EPROM do not clash as the XDATA device is only active during a request from the 8051 pins named READ or WRITE, whereas the CODE device only responds when the PSEN pin is low. The name indicates that the main function of the EPROM is to hold the program. In fact, the external EPROM is only enabled when a pin on the 8051 named the PSEN (program store enable) is pulled low. The external EPROM device (C:0000) is not enabled during RAM access. It is useful in that it can be both accessed byte-wise by the normal MOV instructions and addressed by special bit-orientated intructions, as shown below:

This is a 16 byte (128 bit) area, starting at 020H in the direct segment. This addressing mode is used to access the indirectly addressable on-chip memory above 80H and as an alternative way to get at the direct memory below this address.Ī variation on DATA is BDATA (bit data). MOV R0,#0A0H Put the value held in IDATA location 0A0H into This addressing mode (direct) is the basis of the MOV A,40 Put value held in location 40 into the accumulator. The answer is in the 8051 hardware: When the cpu intends to access D:00, the on-chip RAM is enabled by a purely internal READ signal - the external /RD pin is unchanged. The obvious question is: "How does the 8051 prevent an access to C:0000 resulting in data being fetched from D:00?" Here an 8 bit register (R0) is used to access this area, termed PDATA. Finally, 256 bytes of XDATA can also be addressed in a paged mode.

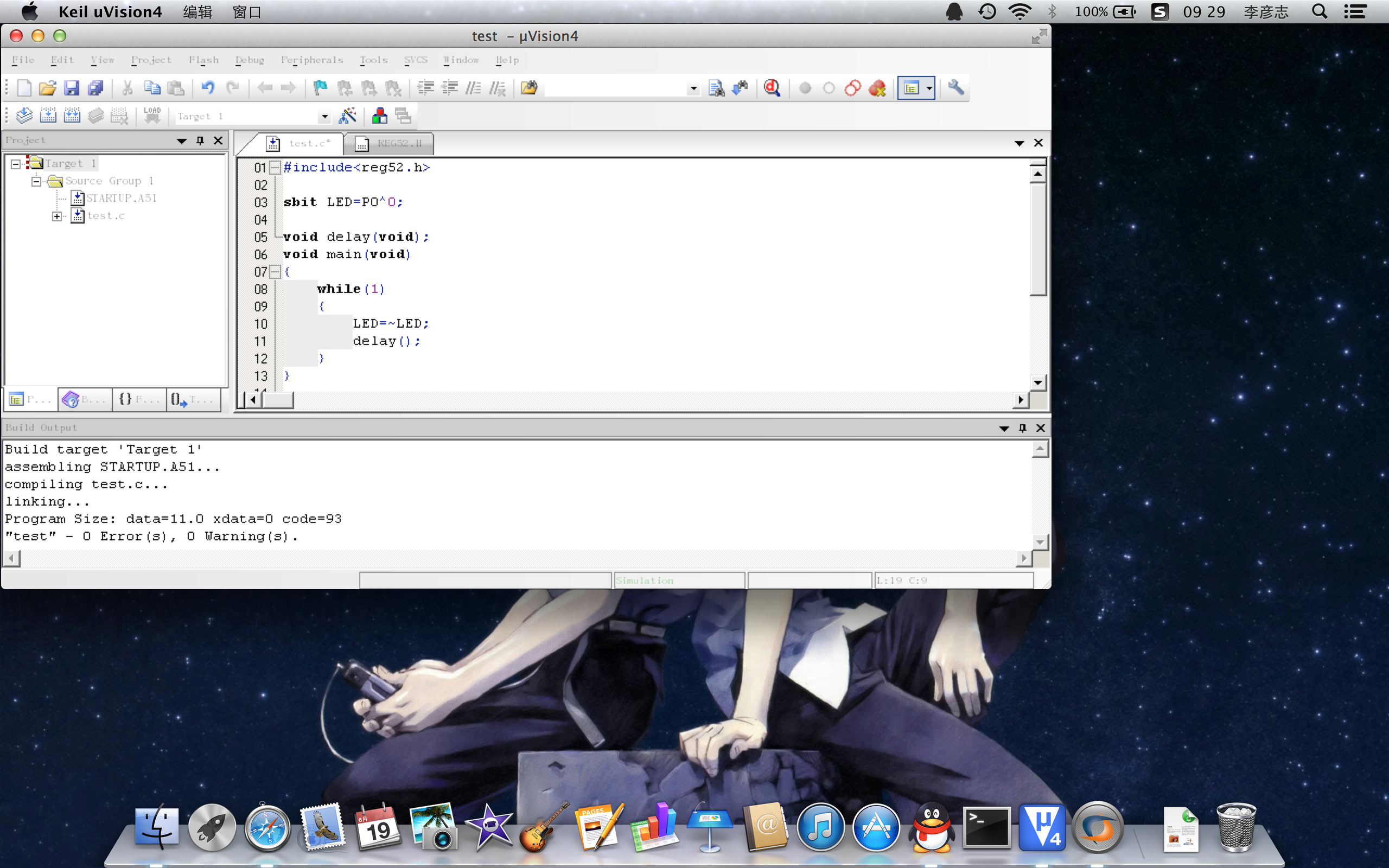

The 8051's only 16 bit register, the DPTR (data pointer) is used to access the XDATA. The 'X:' prefix implies the external XDATA segment. This exists in an external RAM device and, like the C:0000 segment, can extend up to X:0FFFFH (65536 bytes). Obviously, being ROM, only constants can be stored here.Ī fourth memory area is also off-chip, starting at X:0000. The CODE segment is accessed via the program counter (PC) for opcode fetches and by DPTR for data. It typically runs from C:0000 to C:0FFFFH (65536 bytes) but as it is held within an external EPROM, it can be any size up to 64KB (65536 bytes). Just to confuse things, the normal directly addressable RAM from 0-80H can also be indirectly addressed by the MOV instruction!Ī third memory space, the CODE segment, also starts at zero, but this is reserved for the program. As it is only indirectly addressable, it is best left for stack use, which is, by definition, always indirectly addressed via the stack pointer SP. This constitutes an extended on-chip RAM area and was added to the ordinary 8051 design when the 8052 appeared. It is only accessible via indirect addressing (MOV and effectively overlays the directly addressable sfr area. However, a second memory area exists between 80H and 0FFH which is only indirectly addressable and is prefixed by I: and known as IDATA. Above 80H the special function registers are located, which are again directly addressable. It is directly addressable, so that instructions like 'MOV A,x' are usable. This RAM can be used for program variables. This starts at D:00 (the 'D:' prefix implies DATA segment) and ends at 07fH (127 decimal). Within the CPU there is one such, the DATA on-chip RAM. Other microcontrollers, such as the 68HC11, have a single Von Neuman memory configuration, where memory areas are located at sequential addresses, regardless of in what device they physically exist. Perhaps the most initially confusing thing about the 8051 is that there are three different memory spaces, all of which start at the same address. The most basic decision to be made is which memory model to use.įor general information on the C language, number and string representation, please refer to a standard C textbook such as K & R 2.1 8051 Memory Configurations 2.1.1 Physical Location Of The Memory Spaces However, to get the best from it, some appreciation of the underlying hardware is desirable. The Keil C51 compiler has been written to allow C programmers to get code running quickly on 8051 systems with little or no learning curve.

#C51 keil Pc

Thank you for visiting the best get into pc site.2 Keil C51 Compiler Basics - The 8051 Architecture I’m sure you will found get into pc very helpful. If you have any questions, about this post, you can comment on this. You can get Keil C51 Compiler form our site, which is fully working and tested.

#C51 keil 64 Bit

#C51 keil full

#C51 keil Offline

0 kommentar(er)

0 kommentar(er)